Linear delay model in VLSI

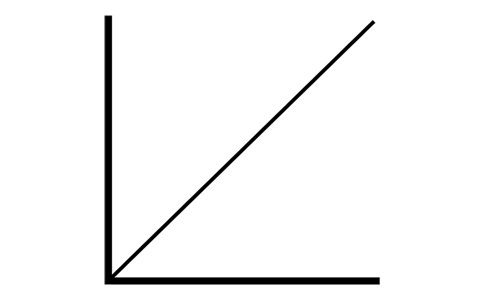

This post tells about logical effort and parasitic delay in linear delay model in VLSI. As was shown before delay linearly depends on the fan-out of the gate.

Normalised delay of a gate can be expressed as the sum of parasitic delay and effort delay . The effort delay depends on the fan-out of the gate , here is a logical effort.

What is fan-out or electrical effort? Situation when a gate is driving identical to itself gates is said to have an electrical effort or fan-out . In case if the load consist of gates different from driving gate, the electrical effort of fan-out can be found by formula , here is the capacitance of the driving gate, and is the capacitance of the load gates that are being driven.

Logical effort of the gate is the ratio of the input capacitance of the gate to the input capacitance of the inverter that delivers the same output current.

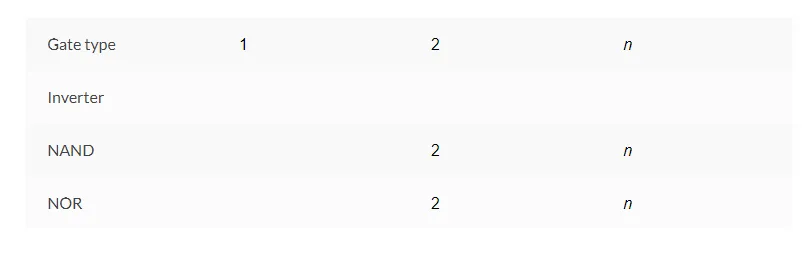

Here logic efforts of the common gates are listed below:

|

Parasitic delay of the gate, is the delay when the gate drives zero load. It is comfortable to use the term of normalised parasitic delay, which is the ratio of diffusion capacitance to the gate capacitance of certain process. The table below shows parasitic delays for the most common gates.

Information about the parasitic delay is important for estimating gate delay. But as soon as the number of inputs growing, the parasitic delay grows steadily.

The delay has squared grows as soon as number of series transistors grows. It means it is better to divide large gate into smaller gates.

The Elmore delay for the complex gate can be calculated as .