Tinkering with Logic Gates Things to like about CMOS gates:

![]() easy to translate logic to fets

easy to translate logic to fets

![]() rail-to-rail switching

rail-to-rail switching

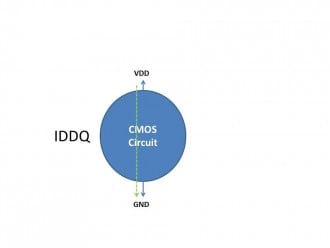

![]() good noise margins, no static power since fets are in cutoff

good noise margins, no static power since fets are in cutoff

![]() sizing not critical to correct operation Things not to like about CMOS gates:

sizing not critical to correct operation Things not to like about CMOS gates:

![]() N inputs Ö 2N fets (i.e., one nfet and one pfet)

N inputs Ö 2N fets (i.e., one nfet and one pfet)

![]() large circuit area, especially for pfets, “heavy” loading of inputs

large circuit area, especially for pfets, “heavy” loading of inputs

![]() pfets are either large or slow relative to nfets

pfets are either large or slow relative to nfets

![]() series connections can get very slow We can replace pfet pullup network with pseudo-NMOS load (pfet with grounded gate) but Š dissipate static power when output is low

series connections can get very slow We can replace pfet pullup network with pseudo-NMOS load (pfet with grounded gate) but Š dissipate static power when output is low

![]() have to make load fet small to ensure that VOL is low enough to cut off nfets in next stage

have to make load fet small to ensure that VOL is low enough to cut off nfets in next stage

![]() reduces static power consumption (good!)

reduces static power consumption (good!)

![]() increases output rise time (bad!)

increases output rise time (bad!)

![]() One alternative: dynamic CMOS gates

One alternative: dynamic CMOS gates

Dynamic CMOS Gates

There’s good news and bad news

CMOS Domino Logic

More Domino-style Circuits

Comments are closed.